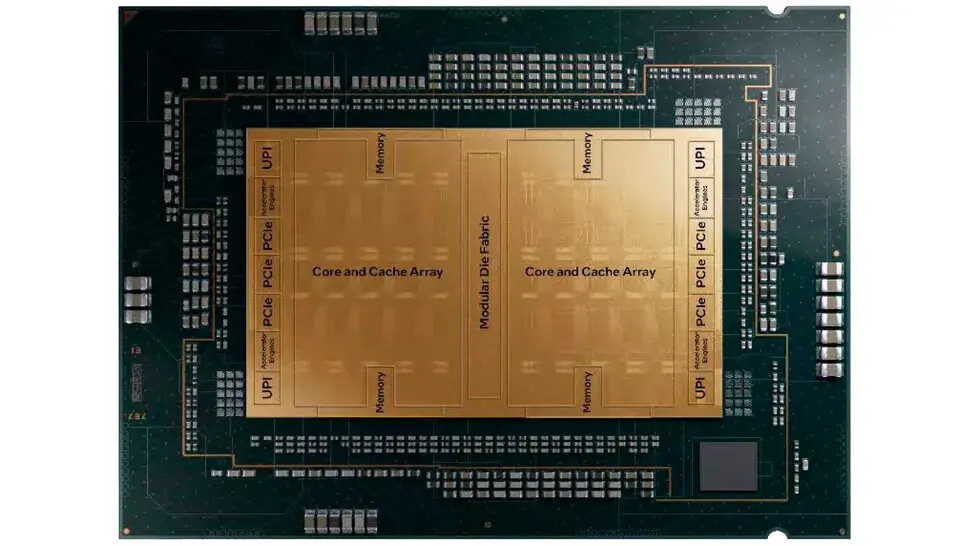

Intel is considering the implementation of large last-level caches on its processors. In an interview with Der8auer and Bens Hardware, Florian Maislinger, a tech communications manager for Intel, mentioned that the company is looking into adding large shared L3 caches to its processors, starting with server processors. Intel is currently developing a new server/workstation processor for 2025 that will feature cache tiles to enhance the shared L3 cache, specifically targeting technical computing workloads similar to those handled by AMD's EPYC "Genoa-X" processors and upcoming "Turin-X" processors.

AMD's "Genoa-X" processors utilize stacked 3D V-Cache on each of the up to 12 "Zen 4" CCDs, significantly boosting performance in cache-sensitive applications like the Ansys suite and OpenFOAM.

While the server processor with a large last-level cache is expected to be released in 2025, there are no plans for similar enhancements to Intel's client processors like the Core Ultra "Arrow Lake-S" in the same year. The recently launched "Arrow Lake-S" desktop processors do not offer a significant gaming performance improvement compared to the 14th Gen Core "Raptor Lake Refresh." Intel has acknowledged the gaming performance issues and is working on updates, potentially in the form of new microcode or changes at the OS-vendor level, to address these concerns and enhance the gaming performance of "Arrow Lake-S."