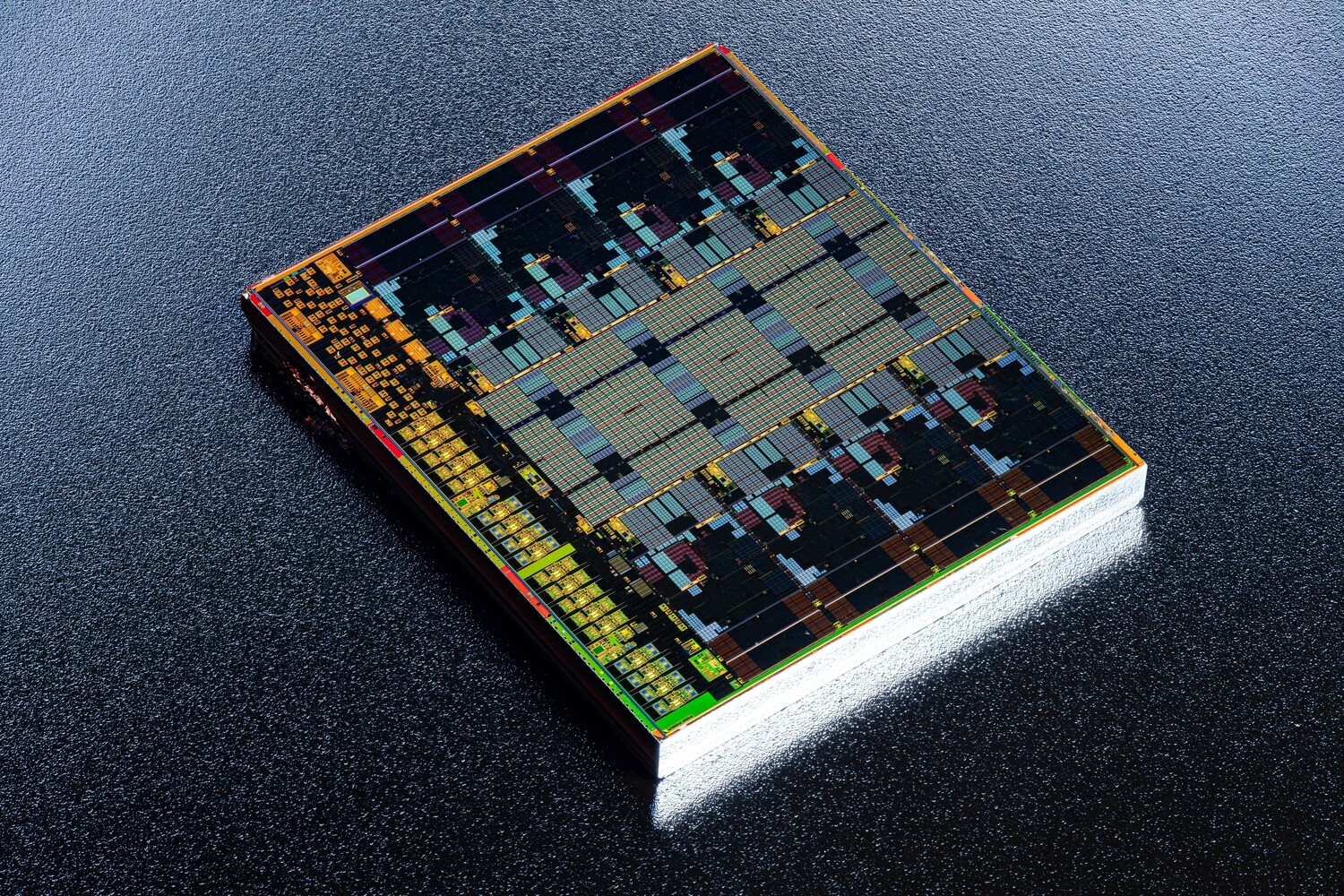

High-Resolution Die-Shots of AMD "Zen 5" 8-Core CCD

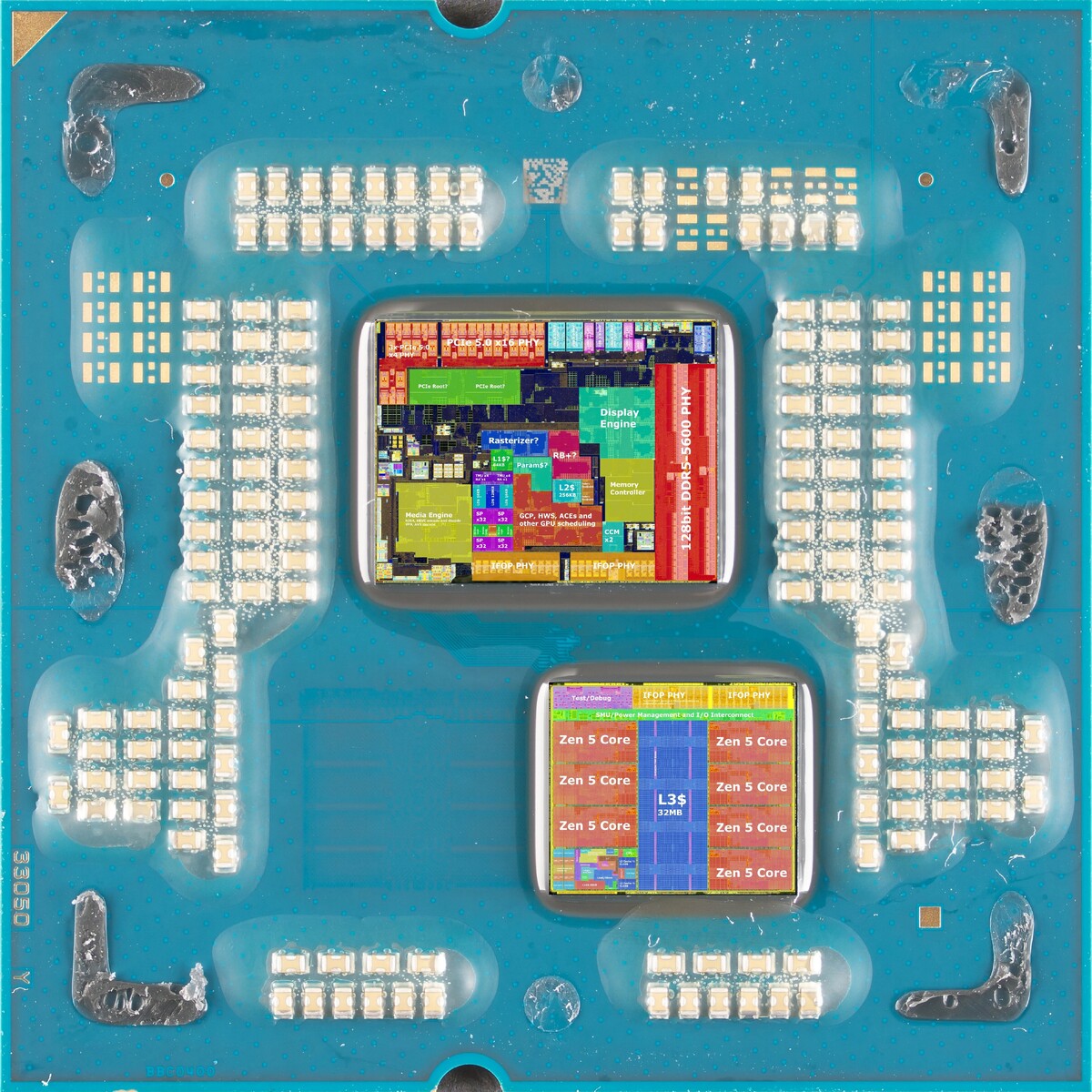

Recently, Nemez, Fitzchens Fitz, and HighYieldYT released high-resolution die-shots of the AMD "Zen 5" 8-core CCD, providing detailed annotations. These images offer a close look at the silicon and its various components, especially the new "Zen 5" CPU core featuring a 512-bit FPU. The "Granite Ridge" package resembles the "Raphael" design, housing up to two 8-core CPU complex dies (CCDs) depending on the processor model, along with a centrally located client I/O die (cIOD) carried over from "Raphael" to minimize product development costs for AMD in the uncore portion of the processor. The "Zen 5" CCD is manufactured on the TSMC N4P (4 nm) foundry node.

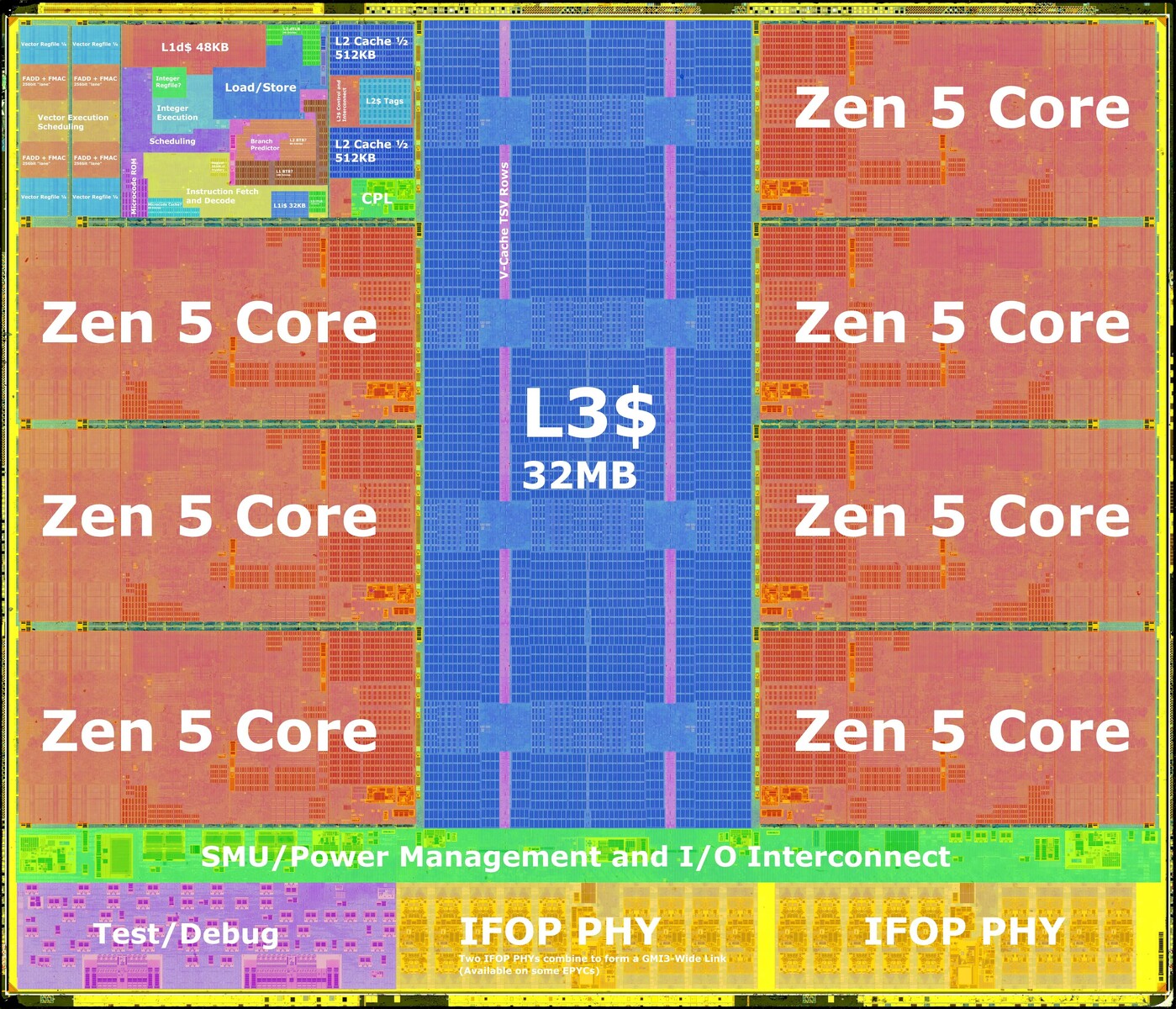

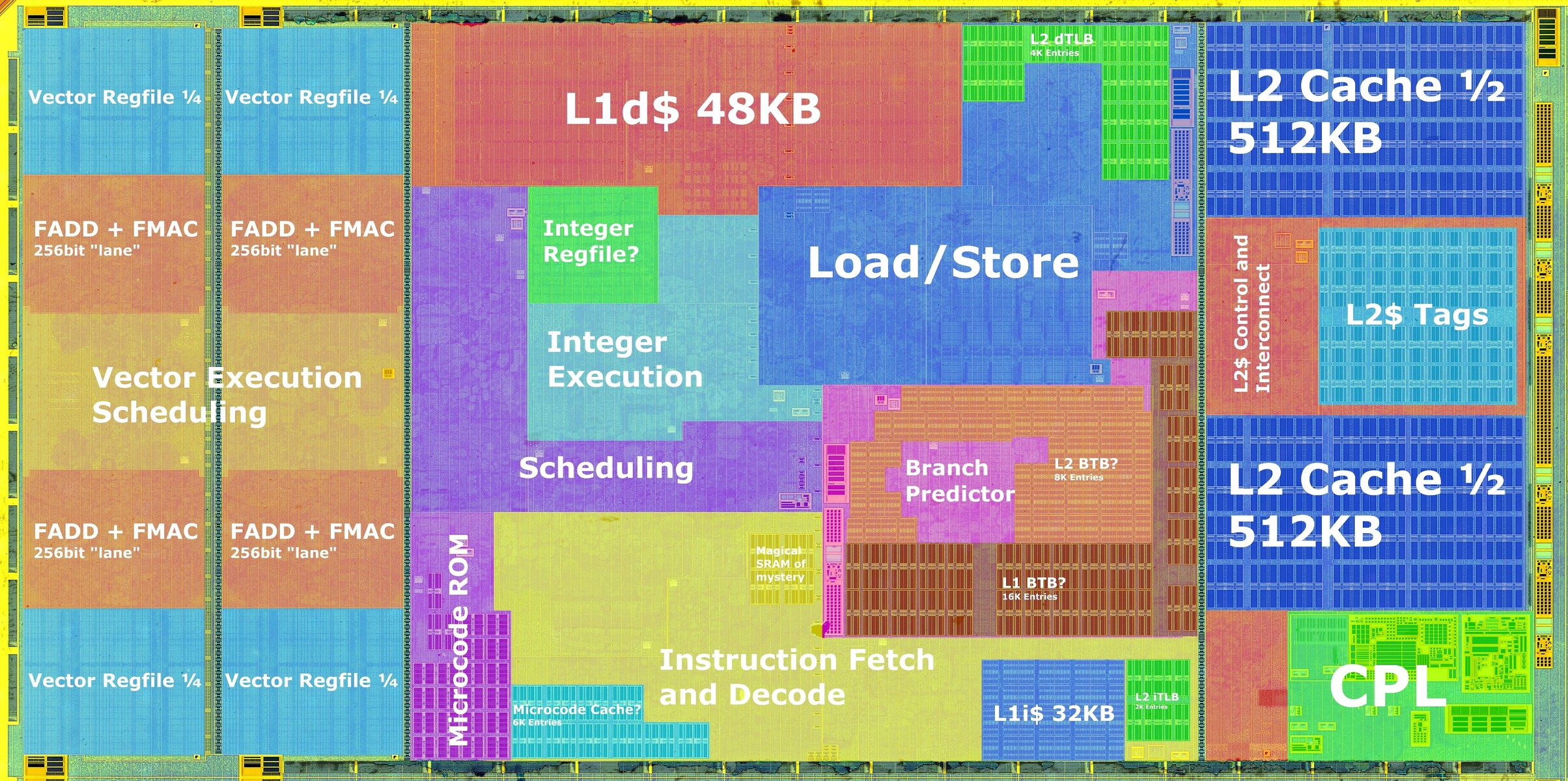

The "Granite Ridge" package positions up to two "Zen 5" CCDs closer together compared to the "Zen 4" CCDs on "Raphael." Each CCD contains 8 full-sized "Zen 5" CPU cores with 1 MB of L2 cache, and a centrally located 32 MB L3 cache shared among all eight cores. Additional components include an SMU (system management unit) and the Infinity Fabric over Package (IFoP) PHYs connecting the CCD to the cIOD. The physical size of each "Zen 5" CPU core is larger than the "Zen 4" core due to the 512-bit floating point data-path, with the Vector Engine pushed to the edge of the core.

The central region of the "Zen 5" core houses the 32 KB L1I cache, 48 KB L1D cache, Integer Execution engine, and the front-end of the processor with Instruction Fetch & Decode, Branch Prediction unit, micro-op cache, and Scheduler. The 32 MB on-die L3 cache features rows of TSVs for potential stacked 3D V-cache, connecting with the CCD's ringbus to create a contiguous 64 MB 3D V-cache with the on-die L3 cache.

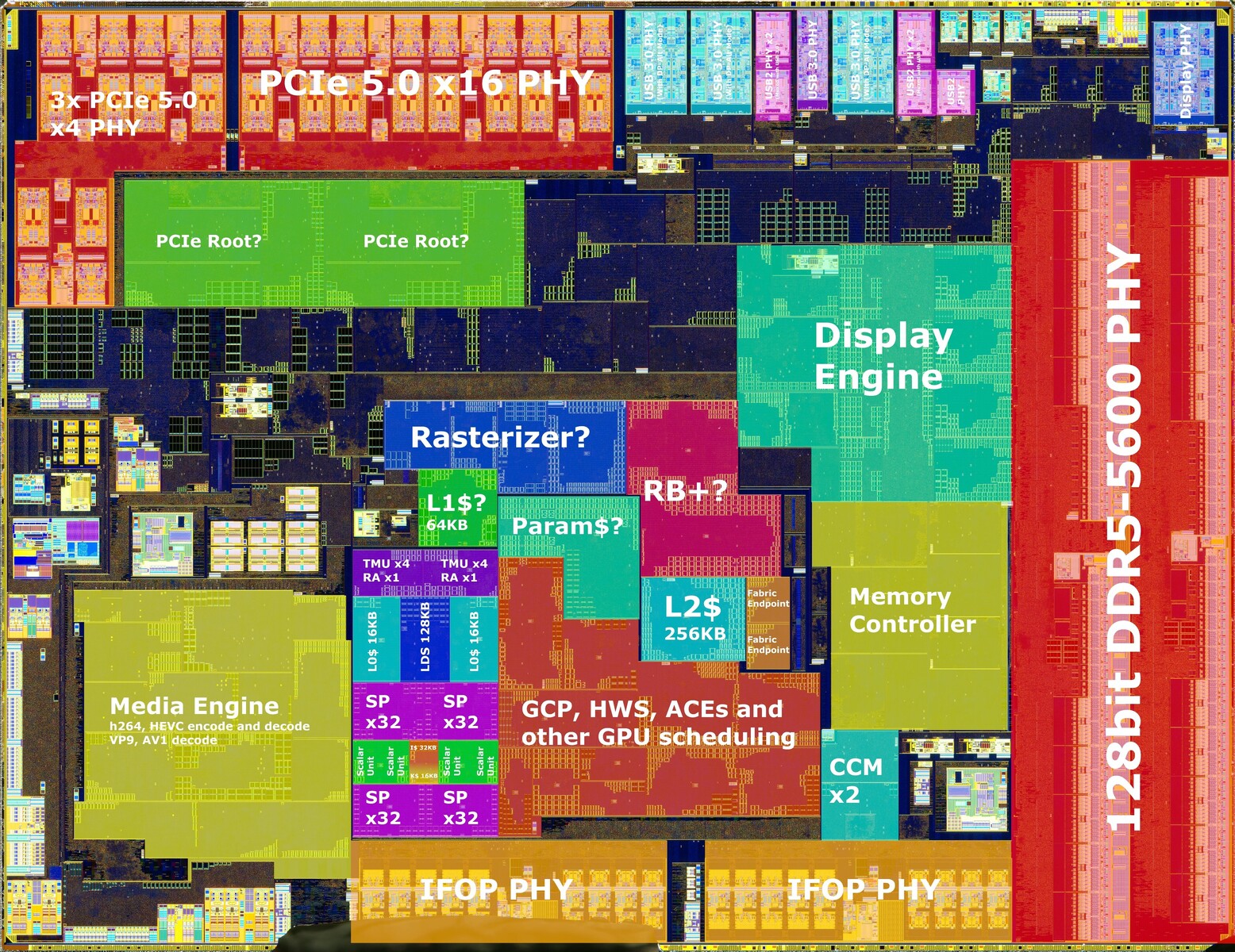

Lastly, the cIOD remains unchanged from "Raphael," built on the TSMC N6 (6 nm) node. The iGPU and its components, including the media acceleration engine and display engine, occupy nearly 1/3rd of the die-area. The iGPU is based on the RDNA 2 graphics architecture, featuring one workgroup processor (WGP) for two compute units (CU) or 128 stream processors. Key components on the cIOD include the 28-lane PCIe Gen 5 interface, two IFoP ports for the CCDs, SoC I/O with USB 3.x and legacy connectivity, and the DDR5 memory controller with a dual-channel (four sub-channel) memory interface.